레지스터

레지스터(이하 Reg)는 다수비트의 데이터를 저장하는 목적으로 사용하는 소자입니다.

1. 공통 클럭을 갖는 다수의 FF을 묶어서 만듭니다.

2. 이진데이터를 저장하기 위해 사용합니다.

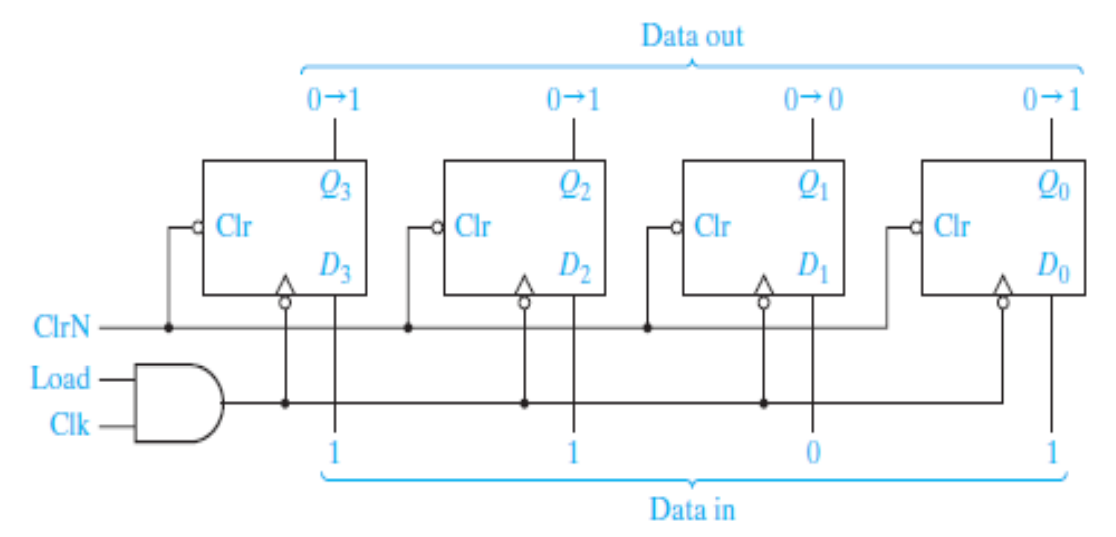

4비트 D-FF으로 구성한 Reg

위 ClrN은 Clear입력이 NOT 게이트를 거쳐서 들어간다는 뜻입니다.

Load를 1로 만들어준 상태에서 클럭입력이 하강에지가 되면,

D-FF의 출력에 입력이 나타나게 됩니다.

하지만 위와같이 구성된 reg를 사용하게 되면, 게이트를 통과하면서 생기는 시간 지연으로

모든 FF에서 동시에 값의 저장이 일어나지 않을 수 있습니다.

또한 클럭입력의 에지에서 값의 변화가 일어날 수도 있지만,

Load신호에 의해서도 FF 출력에 변화가 일어날 수 있습니다.

여기서 클럭활성화(Clock Enable, CE)입력을 D-FF에 만들어주게되면

굳이 Load와 Clk으로 게이트 입력을 만들어 FF의 클럭입력에 연결하지 않아도 됩니다.

따라서 CE가 0일때는 현재 FF의 출력으로 나가는 값이 계속해서 다음 상태가 되고,

CE가 1일때는 정상적으로 작동하여 입력이 다음 상태가 되도록 합니다.

따라서 Load입력과 함께 클럭입력을 제어하는 것이 아니라,

CE에 Load입력을 줌으로써 클럭입력은 그대로 두고,

오직 CE를 통해서만 값의 저장을 결정하도록 합니다.

Shift Reg

Shift reg는 2진 데이터를 저장하고 있으면서, Shift 신호가 들어오면

좌, 후로 데이터가 밀려가는 기능을 가집니다.

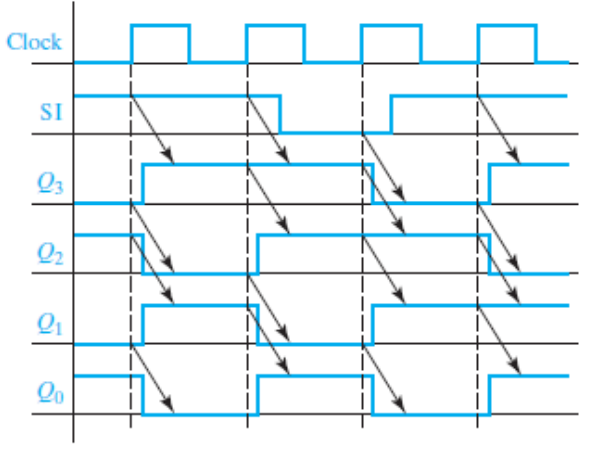

직렬입력-직렬출력 4비트 Shift Reg

4개의 상승-에지트리거 D-FF으로 이루어져 있고,

맨 왼쪽 D-FF의 입력에는 SI(Serial in)입력이 주어져있습니다.

만약 SI입력을 따로 주지 않고, SO(Serial out)입력과 연결시키면, 순환형으로 만들 수 있습니다.

Shift입력이 FF의 CE에 연결되어있고, 활성화 시킨 상태에서

클럭입력의 상승에지에 맞춰 SI입력이 우측으로 이동하게 됩니다.

타이밍도를 보면 $Q_3 ~ Q_0$에는 기존입력이 들어있고,

클럭의 상승 에지에 맞춰 오른쪽으로 이동된다는 것을 알 수 있습니다.

위와 같이 구성된 Shift reg는 직렬입력-직렬출력 Shift reg라고 불리며

FF의 개수가 n개라면, n번의 클럭 주기 이후 출력(SO)에 반영되게 됩니다.

또한 모든 입력이 다 나오려면 n번의 클럭 주기가 있어야함을 알 수 있습니다.

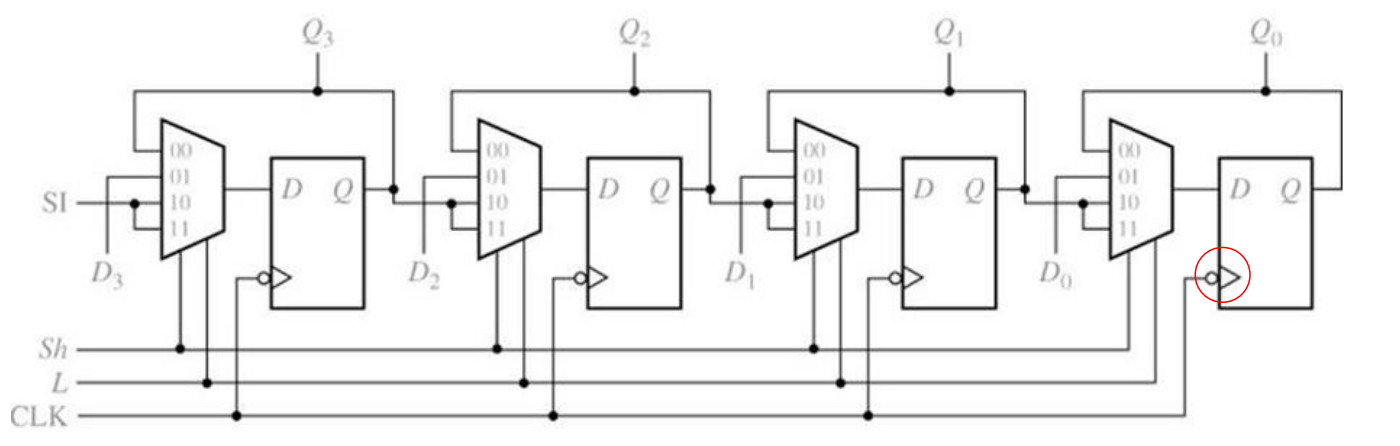

병렬입력-병력출력 Shift Reg

병렬입력-병렬출력 Shift Reg는 Shift기능과 병렬입력 기능을 모두 가지고 있는 소자입니다.

병렬로 데이터를 저장한 후, 직렬로 데이터를 저장하는 회로에 많이 사용됩니다.

이번 reg는 데이터를 shift하거나 저장 또는 현 상태를 유지시켜야합니다.

따라서 이러한 기능의 분리를 위해, MUX를 활용하여 FF을 제어하게 됩니다.

Shift Enable과 Load Enable 신호를 통해 MUX를 제어하고 있습니다.

또한 MUX의 0번 입력에는 Q의 출력을 피드백으로 연결시켜

0번일때는 현 상태를 유지시킨다는 것을 알 수 있습니다.

눈여겨 볼 부분은, 2~3번 입력이 모두 SI입력이라는 점인데

$Load = Shift = 1$인 경우를 Shift로 처리했음을 알 수 있습니다.

$t_5$부터는 Shift 신호가 0이라 현 상태가 유지되고 있음을 확인 할 수 있습니다.

병렬입력-병렬출력은 직렬입력-직렬출력과는 다르게,

입력을 병렬로 저장하고, 바로 다음 클럭부터 출력에 반영됩니다.

'CS > 논리회로' 카테고리의 다른 글

| [논리회로] 무어머신과 순차 패리티 체커 회로 (0) | 2022.06.11 |

|---|---|

| [논리회로] 카운터 (0) | 2022.06.11 |

| [논리회로] 플립플롭 (0) | 2022.06.10 |

| [논리회로] 래치와 투과성 문제 (0) | 2022.06.10 |

| [논리회로] ROM과 PLA (0) | 2022.06.09 |