ROM

ROM은 Read only memory의 줄임말로 말 그대로 읽기만 가능한 메모리입니다.

따라서 변경이 불가능합니다.

이진 데이터 배열을 저장하는 것이 목적이며, 이를 위해 반도체 소자의 연결로 구성되어 있습니다.

ROM은 n개의 입력 라인과 m개의 출력 라인을 갖습니다.

n개의 입력라인이므로 총 $2^n$개의 입력을 만들 수 있고

각각의 입력에 대응되는 m비트의 배열을 워드라고 불립니다.

이때 m비트를 워드의 길이라고 합니다.

$2^n \times m$비트 ROM은 $2^n$개의 행과 m개의 열을 갖는 진리표를 저장할 수 있기 때문에

n변수의 m개의 함수를 구현할 수 있게됩니다.

ROM의 기본적인 구조

ROM은 디코더와 메모리 배열로 구성됩니다.

길이가 n인 입력이 디코더에 들어오면, $2^n$개의 출력 중 단 한개의 출력만이 1이 되어 메모리 배열에 입력됩니다.

디코더의 출력에 따라 메모리 배열은 한개의 워드를 선택하고, 이 워드의 비트 패턴이 메모리 출력 라인으로 전송됩니다.

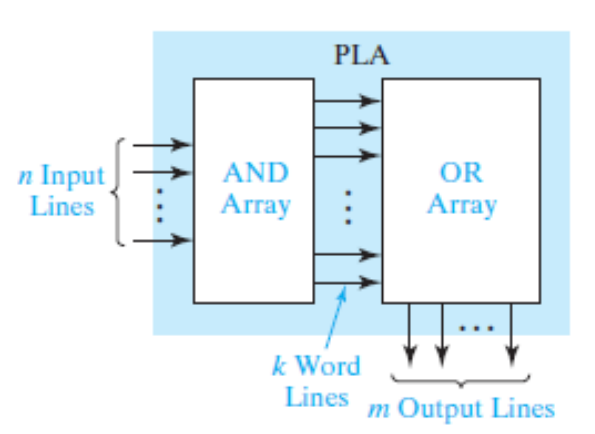

PLA

PLA는 Programmable Logic Array의 줄임말입니다.

PLA는 다양한 논리 함수를 제공하도록 프로그램이 가능한 디지털 집적회로들을 말합니다.

PLA를 구조를 보면 ROM과 동일한 기능을 수행한다는 것을 알 수 있습니다.

CPLD

CPLD는 Complex Programmable Logic Device의 약자입니다.

여러개의 PLA가 한개의 칩에 들어있고, 서로 연결되어있는 구조입니다.

FPGA

FPGA는 Field Programmable Gate Array의 약자입니다.

프로그램이 가능한 연결선들과 함께 동일한 기능을 가지는 논리 셀들의 배열을 가지는 집적회로입니다.

유저는 각 논리 셀과 이들간의 연결을 통해 함수를 구현할 수 있습니다.

내부는 CLB(Configurable Logic Block)라고 부르는 논리 셀들의 배열로 구성되어 있습니다.

또한 CLB의 배열은 입출력 인터페이스 블록으로 둘러싸여있습니다.

'CS > 논리회로' 카테고리의 다른 글

| [논리회로] 카운터 (0) | 2022.06.11 |

|---|---|

| [논리회로] 레지스터 (0) | 2022.06.10 |

| [논리회로] 플립플롭 (0) | 2022.06.10 |

| [논리회로] 래치와 투과성 문제 (0) | 2022.06.10 |

| [논리회로] MUX와 디코더 (0) | 2022.06.09 |